Trace length tuning: because making your PCB look like a racetrack is totally a feature, not just a necessity!

- protowoerk

- Jan 29, 2025

- 2 min read

When developing new hardware from scratch, particularly when working with high-speed devices like LCD interfaces, SDRAM, SDCARD, and others, the process can be challenging. Routing the traces for these components requires additional care to ensure that the timing specifications are met and that the final product performs reliably.

At our lab, we've compiled a set of "rules of thumb" to guide us through the complex process of designing PCBs for high-speed devices. These guidelines help us navigate the designier in trace routing and signal integrity, ensuring that our designs meet the necessary specification. Here's a peek into our approach:

For high-speed data lines, it's crucial to use a multilayer PCB (4-6 layers) with a solid ground (GND) reference under the high-speed traces. This helps in minimizing noise and ensuring signal integrity.

Ensuring that the trace impedance (50/90/110ohm ..etc) matches the interface requirements is essential. This minimizes reflections and signal loss, which are critical for maintaining data integrity at high speeds

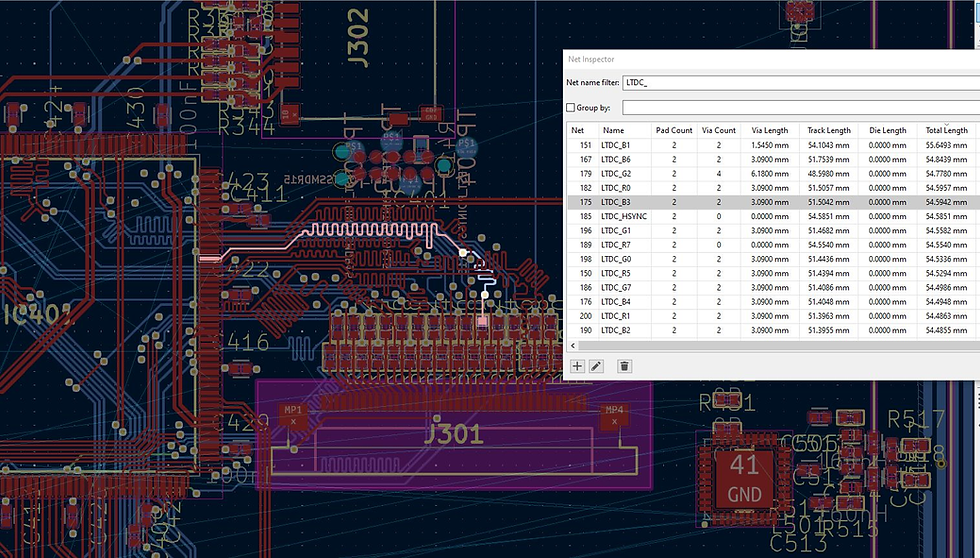

To minimize board skew, it’s vital to keep the trace lengths equal between the data and clock signals. Specifically, the clock traces should be matched to the data/address group traces within ±10mm. This ensures synchronized data transfer and reduces timing errors.

Limiting the maximum trace length to below 120mm helps in reducing signal degradation and timing delays, which are particularly important in high-speed circuits.

Placing clock signals on an internal layer can significantly reduce electromagnetic interference (EMI). Additionally, routing the clock signal at least 3x the trace width away from other signals minimizes crosstalk and noise.

Whenever a trace changes layers, it’s recommended to place a ground via next to the signal via. This provides a return path for the ground current, reducing the risk of signal integrity issues.

Comments